# SpaceWire (2013)

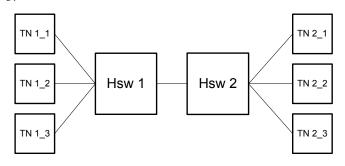

Fifth International Conference 10<sup>th</sup> - 14<sup>th</sup> of June 2013 Gothenburg, Sweden

2013.spacewire-conference.org

Together ahead. **RUAG**

## SpaceWire-2013

## Proceedings of the 5<sup>th</sup> International SpaceWire Conference Gothenburg 2013

Editors: Steve Parkes and Carole Carrie

Space Technology Centre University of Dundee SpaceWire-2013

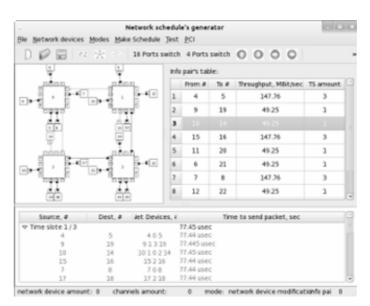

**Proceedings of International SpaceWire Conference**

Gothenburg 2013

ISBN: 978-0-9557196-4-6

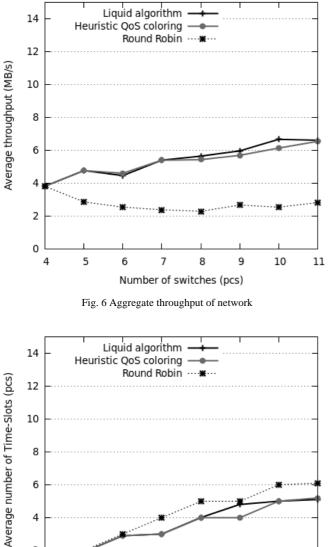

Space Techology Centre University of Dundee © Space Technology Centre University of Dundee Dundee 2013

All rights reserved. No part of this publication may be reproduced or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

#### Preface

These proceedings contain the papers presented at the 2013 International SpaceWire Conference, held in the Radisson Blu Scandinavia Hotel, Gothenburg, Sweden, between 10 and 13 June, 2013. The International SpaceWire Conference aims to bring together SpaceWire product designers, hardware engineers, software engineers, system developers and mission specialists interested in and working with SpaceWire to share the latest ideas and developments related to SpaceWire technology. SpaceWire technology is now being used or designed into over one hundred spacecraft, covering science, exploration Earth observation and commercial applications. High profile missions like James Webb Space Telescope, Astro-H, GAIA, ExoMars, Bepicolombo, Sentinels 1, 2, 3 and 5 precursor, and GOES-R are using SpaceWire extensively. SpaceWire is being used in Europe, Japan, USA, Russia, China, India, and other countries of the World.

The conference covers many different aspects of SpaceWire technology and includes both academic and industrial presentations. Sessions address recent developments of the SpaceWire set of standards, space missions and other applications using SpaceWire, new components, sensors and cables which support the SpaceWire standard; products supporting SpaceWire including onboard equipment, instruments and related onboard software; methods and equipment to aid the test and verification of SpaceWire components, units and systems; and SpaceWire networks, their architecture, configuration, and discovery, as well as "plug and play" concepts, other higher level protocols and related hardware and software design issues. A technical seminar on SpaceWire at the conference was presented by several world leading experts on SpaceWire providing hints and tips on using SpaceWire based on many years' experience.

The community of engineers working on SpaceWire meet regularly at the SpaceWire Working Group meetings to help with the further development of SpaceWire and related standards and technologies. This group includes engineers from many parts of the World with substantial contributions from Europe, Japan, Russia and the USA. The SpaceWire Conference complements these Working Group meetings with more formal presentations from a wider range of contributors.

There is growing interest in the SpaceFibre which aims to provide multi-gigabit/s network technology for future space flight application like high-resolution multi-spectral imaging and synthetic aperture radar. A second seminar introduced and demonstrated SpaceFibre technology which can operate over both electrical and fibre-optic media. A growing number of papers in the conference addressed SpaceFibre.

The conference committee would like to acknowledge the support and hard work of the many individuals who made International SpaceWire Conference 2013 a reality. First, we thank the authors and the keynote speakers for their high-quality contributions. We express our gratitude to the Technical Committee for their assistance in the review process. We thank all people supporting us at Aeroflex, the Space Technology Centre at the University of Dundee and the European Space Agency.

The Conference Chairpersons,

Martin Suess, European Space Agency, The Netherland Steve Parkes, Space Technology Centre, University of Dundee, UK Sand Habinc, Aeroflex Gaisler, Sweden Teresa Farris, Aeroflex, USA

## **Technical Committee**

Allison Bertrand - South West Research Institute, USA Yohann Bricard - Atmel Omar Emam - Astrium, UK Wahida Gasti - ESA, The Netherlands Viacheslav Grishin - Submicron Sandi Habinc - Aeroflex Gaisler Omar Haddad – Dell, USA Hiroki Hihara – NEC, Japan Christophe Honvault - ESA Torbjörn Hult - RUAG Space, Sweden Jørgen Ilstad - ESA, The Netherlands Paul Jaffe - Naval Research Laboratory, USA David Jameux- ESA, The Netherlands Gerald Kempf - RUAG Space, Austria Clifford Kimmery – Honeywell Inc. Alexander Kisin - MEI, USA Robert Klar - South West Research Institute, USA Jerome Lachaize - Astrium, France Jennifer Larsen - Aeroflex Jim Lux - NASA JPL, USA Peter Mendham - Scisys Ltd., UK Masaharu Nomachi - University of Osaka, Japan Olivier Notebaert - Astrium SAS, France Steve Parkes - University of Dundee, Scotland, UK Manuel Prieto - Alcala University, Spain Paul Rastetter - Astrium GmbH, Germany Josep Rosello - ESA Derek Schierlmann - Naval Research Laboratory, USA Alan Senior - SEA, UK Yuriy Sheynin - St. Petersburg State University of Aerospace Instrumentation, Russia Tatiana Solokhina - ELVEES, Russia Martin Suess - ESA, The Netherlands Tadayuki Takahashi - JAXA Antonis Tavoularis - Teletel Raffaele Vitulli - ESA, The Netherlands Takahiro Yamada - JAXA/ISAS, Japan Takayuki Yuasa – JAXA, Japan

#### Monday 10 June

- 15:30-19:00 Registration

- 16:00 18:00 Tutorials of SpaceWire and SpaceFibre

#### Tuesday 11 June

- 09:00 10:00 Conference Opening / Keynote Presentations (60 min)

- 10:00 10:50 Standardisation 1 (50 min)

- 11:10-12:25 Standardisation 2 (75 min)

- 13:45 15:25 Test & Verification 1 (100 min)

- 15:45 17:00 Onboard Equipment & Software (75 min)

#### Wednesday 12 June

- 09:00 10:55 Components 1 (115 min)

- 11:15-12:05 Components 2 (50 min)

- 12:05 12:35 Onboard Equipment & Software (30min)

- 13:55 15:10 Networks & Protocols (75 min)

- 15:10 16:40 Poster Session (90 min)

#### Thursday 13 June

- 09:00-09:45 Standardisation (45 min)

- 09:45 10:45 Test & Verification (60 min)

- 11:05 12:35 Missions & Applications (90 min)

- 13:55 15:10 Components (75 min)

- 15:30 17:10 Networks & Protocols (100 min)

Programme is subject to change

## SpaceFibre: Multiple Gbit/s Network Technology with QoS, FDIR and SpaceWire Packet Transfer Capabilities

SpaceWire Standardisation, Long Paper

Steve Parkes, Chris McClements, Space Technology Centre, University of Dundee, Dundee, DD1 4EE, UK sparkes@computing.dundee.ac.uk Albert Ferrer, Alberto Gonzalez, STAR-Dundee STAR House, 166 Nethergate, Dundee, DD1 4EE, UK

*Abstract*— SpaceFibre is a very high-speed serial link designed specifically for use onboard spacecraft. It carries SpaceWire packets over virtual channels and provides a broadcast capability similar to SpaceWire time-codes but offering much more capability. SpaceFibre operates at 10 times the data-rate of SpaceWire, can run over fibre optic or electrical media, provides galvanic isolation, includes coherence Quality of Service (QoS) and Fault Detection Isolation and Recovery (FDIR) support, and provides lowlatency signalling. SpaceFibre can run over distances of 5m with copper cable and 100 m or more with fibre optic cable.

SpaceFibre is compatible with the packet level of the SpaceWire standard (ECSS-E-ST-50-12) and is therefore able to run the SpaceWire protocols defined in ECSS-E-ST-50-51C, 52C and 53C. This means that applications developed for SpaceWire can be readily transferred to SpaceFibre.

The aim of SpaceFibre is to provide point-to-point and networked interconnections for very high data-rate instruments, mass-memory units, processors and other equipment, on board a spacecraft.

This paper introduces SpaceFibre, describes the SpaceFibre QoS, FDIR and network level operation of SpaceFibre.

Index Terms—SpaceWire, SpaceFibre, networks, spacecraft onboard processing

#### I. INTRODUCTION

SpaceFibre [1] [2] [3] [4] is a very high-speed serial datalink being developed by the University of Dundee for ESA which is intended for use in data-handling networks for high data-rate payloads. SpaceFibre is able to operate over fibreoptic and electrical cable and support data rates of 2 Gbit/s in the near future and up to 5 Gbit/s long-term. It aims to complement the capabilities of the widely used SpaceWire onboard networking standard [5]: improving the data rate by a factor of 10, reducing the cable mass by a factor of four and providing galvanic isolation. Multi-laning improves the data-rate further to well over 20 Gbits/s.

SpaceFibre provides a coherent quality of service mechanism able to support best effort, bandwidth reserved, scheduled and priority based qualities of service. It substantially improves the fault detection, isolation and recovery (FDIR) capability compared to SpaceWire.

SpaceFibre aims to support high data-rate payloads, for example synthetic aperture radar and hyper-spectral optical instruments. It provides robust, long distance communications for launcher applications and supports avionics applications with deterministic delivery constraints through the use of virtual channels. SpaceFibre enables a common onboard network technology to be used across many different mission applications resulting in cost reduction and design reusability. SpaceFibre uses a packet format which is the same as SpaceWire enabling simple connection between existing SpaceWire equipment and high-speed SpaceFibre links and networks.

The SpaceFibre interface is designed to be implemented efficiently, requiring substantially fewer logic gates than a RapidIO interface. It is currently being prototyped in a range of onboard processing, mass memories and other spacecraft applications. Interoperability tests between independent Japanese and European implementations were carried out successfully in December 2012 and April 2013.

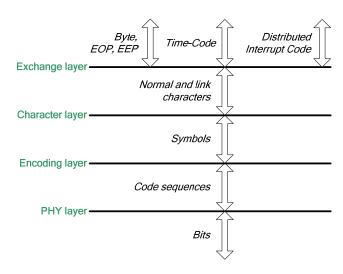

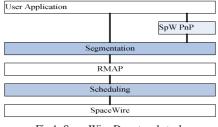

#### II. SPACEFIBRE PROTOCOL STACK

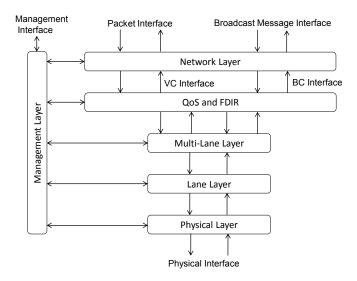

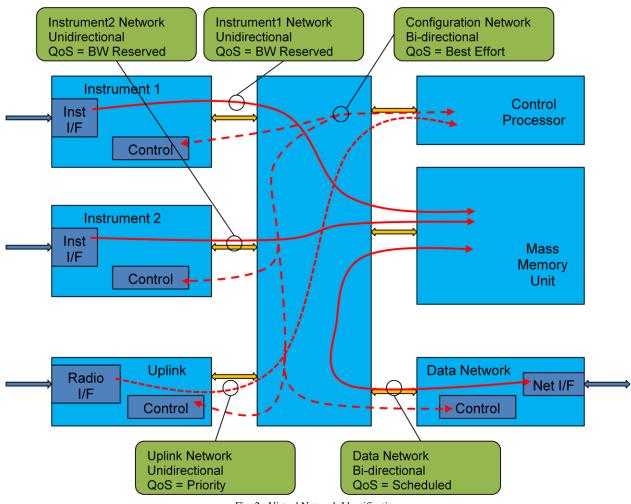

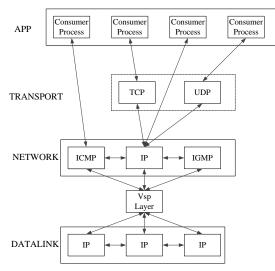

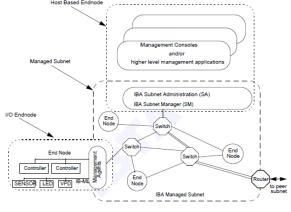

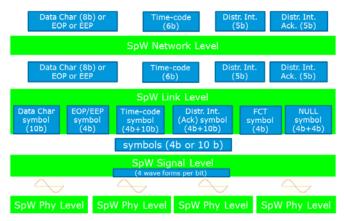

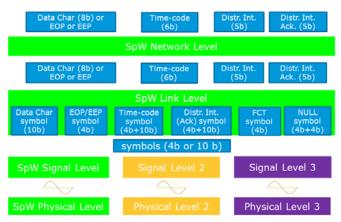

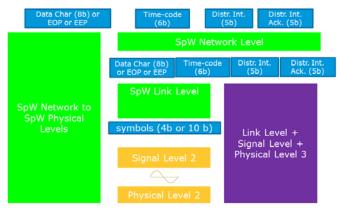

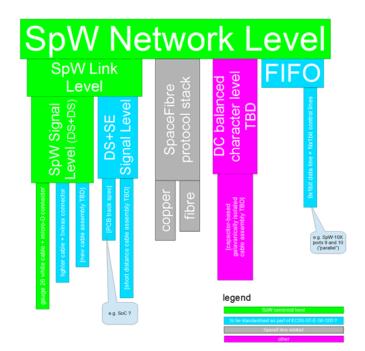

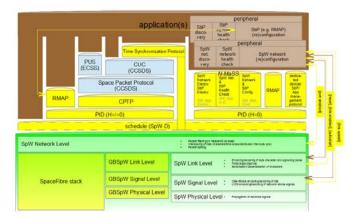

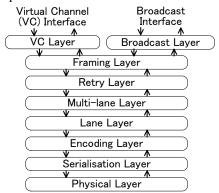

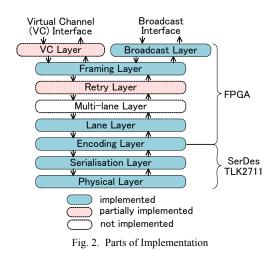

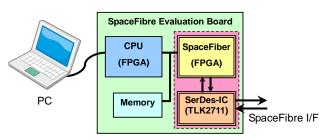

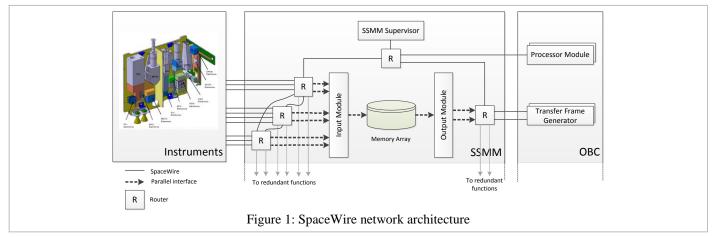

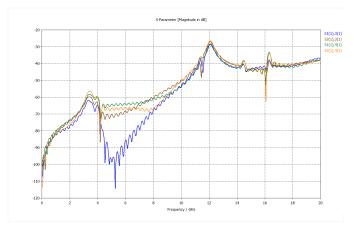

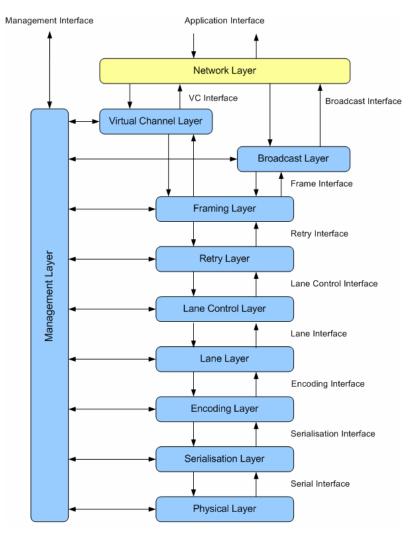

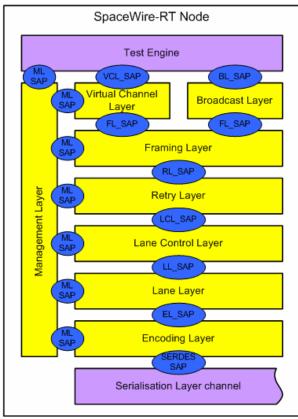

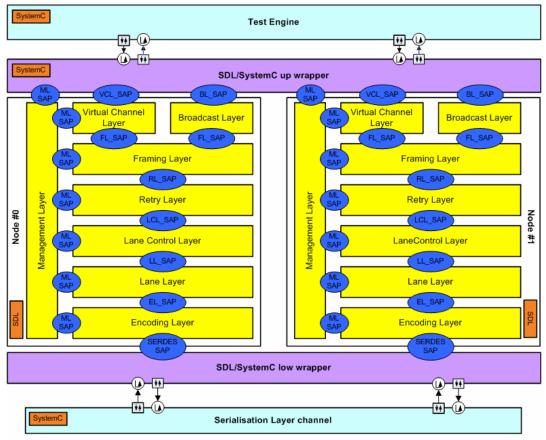

The SpaceFibre protocol stack is illustrated in Figure 1.

#### Figure 1 SpaceFibre Protocol Stack

The network layer protocol is responsible for the transfer of application information over a SpaceFibre network. It provides two services: Packet Transfer Service and Broadcast Message Service. The Packet Transfer Service transfers SpaceFibre packets over the SpaceFibre network, using the same packet format and routing concepts as SpaceWire uses. SpaceFibre supports both path and logical addressing. The broadcast message service is responsible for broadcasting short messages (8 bytes) to all nodes on the network. These messages can carry time and synchronisation signals and be used to signal the occurrence of various events on the network.

The management layer is responsible for configuring, controlling and monitoring the status of all the layers in the SpaceFibre protocol stack. For example it can configure the QoS settings of the virtual channels in the QoS and FDIR layer.

The QoS and FDIR layer is responsible for providing quality of service and managing the flow of information over a SpaceFibre link. It frames the information to be sent over the link to support QoS and scrambles the packet data to reduce electromagnetic emissions. The QoS and FDIR layer also provides a retry capability, detecting any frames or control codes that go missing or arrive containing errors and resending them. With this inbuilt retry mechanism SpaceFibre is very resilient to transient errors.

The Multi-Lane layer is responsible for operating several SpaceFibre lanes in parallel to provide higher data throughput. In the event of a lane failing the Multi-Lane layer provides support for graceful degradation, automatically spreading the traffic over the remaining working links.

The Lane layer is responsible for lane initialisation and error detection. In the event of an error the lane is automatically re-initialised. The Lane layer encodes data into symbols for transmission using 8B/10B encoding and decodes these symbols in the receiver. 8B/10B codes are DC balanced supporting AC coupling of SpaceFibre interfaces.

The Physical layer is responsible for serialising the 8B/10B symbols and for sending them over the physical medium. In the

receiver the Physical layer recovers the clock and data from the serial bit stream, determines the symbol boundaries and recovers the 8B/10B symbols. Both electrical cables and fibre-optic cables are supported by SpaceFibre.

#### III. SPACEFIBRE QUALITY OF SERVICE

A SpaceFibre interface includes a number of virtual channels. Each provides a FIFO type interface like a SpaceWire link. When data from a SpaceWire packet is placed in a SpaceFibre virtual channel it is transferred over the SpaceFibre link and placed in the same numbered virtual channel at the other end of the link. Data from the several virtual channels are interleaved over the physical SpaceFibre connection. To support the interleaving, data is sent in short frames of up to 256 SpaceWire N-chars each. A virtual channel can be assigned a quality of service which determines the precedence with which that virtual channel will compete with other virtual channels for sending data over the SpaceFibre link. Priority, bandwidth reservation, and scheduled qualities of service can be supported all operating together using a simple precedence mechanism.

In this section the SpaceFibre quality of service mechanism is described.

#### A. Frames and Virtual Channels

To provide quality of service, it is necessary to be able to interleave different data flows over a data link or network. If a large packet is being sent with low priority and a higher priority one requests to be sent, it must be possible to suspend sending the low priority one and start sending the higher priority packet. To facilitate this SpaceWire packets are chopped up into smaller data units called frames. When the high priority packet requests to be sent, the current frame of the low priority packet is allowed to complete transmission, and then the frames of the high priority packet are sent. When all the frames of the high priority packet have been sent, the remaining frames of the low priority packet can be sent.

Each frame has to be identified as belonging to a particular data flow so that the stream of packets can be reconstructed at the other end of the link. Low priority packets belong to one data stream and high priority packets belong to another data stream.

Each independent data stream allowed to flow over a data link is referred to as a virtual channel (VC). Virtual channels are unidirectional and have a QoS attribute, e.g. priority. At each end of a virtual channel is a virtual channel buffer (VCB), which buffers the data from and to the application. An output VCB takes data from the application and buffers it prior to sending it across the data link. An input VCB receives data from the data link and buffers it prior to passing it to the receiving application.

There can be several output virtual channels connected to a single data link, which compete for sending information over the link. A medium access controller determines which output virtual channel is allowed to send the next data frame. When an output VCB has a frame of data ready to send and the corresponding input VCB at the other end of the link has room

for a full data frame, the output VCB requests the medium access controller to send a frame. The medium access controller arbitrates between all the output VCBs requesting to send a frame. It uses the QoS attribute of each of the requesting VCBs to determine which one will be allowed to send the next data frame.

Priority is one example of a QoS attribute. Other types of QoS are considered in the subsequent sections.

#### B. Precedence

For the medium access controller to be able to compare QoS attributes from different output VCBs, it is essential that they are all using a common measure that can be compared. The name given to this measure is precedence. The competing output VCB with the highest precedence will be allowed to send the next frame.

#### C. Bandwidth Reservation

When connecting an instrument via a network to a mass memory, what the systems engineer needs to know is "how much bandwidth do I have to transfer data from the instrument to the mass memory?" Once the network bandwidth allocated to a particular instrument has been specified, it should not be possible for another instrument to impose on the bandwidth allocated to that instrument. A priority mechanism is not suitable for this application. If an instrument with high priority has data to send it will hog the network until all its data has been sent. What is needed is a mechanism that allows bandwidth to be reserved for a particular instrument.

Bandwidth reservation calculates the bandwidth used by a particular virtual channel, and compares this to the bandwidth reserved for that virtual channel to calculate the precedence for that virtual channel. If the virtual channel has not used much reserved bandwidth recently, it will have a high precedence. When a data frame is sent by this virtual channel, its precedence will drop. Its precedence will increase again over a period of time. If a virtual channel has used more than its reserved bandwidth recently, it will have a low precedence.

A virtual channel specifies a portion of overall Link Bandwidth that it wishes to reserve and expects to use, i.e. its Expected Bandwidth.

When a frame of data is send by any virtual channel, each virtual channel computes the amount of bandwidth that it would have been permitted to send in the time interval that the last frame was sent. This is known as the Bandwidth Allocation. Bandwidth Allowance is calculated as follows:

$BandwidthA\, llowance = Expected \times LastFrameBandwidth$

Where Expected or Expected Bandwidth Percentage is the portion of overall link bandwidth that a virtual channel wishes to use, and Last Frame Bandwidth is the amount of data sent in the last data frame.

Each virtual channel can use this to determine its Bandwidth Credit, which is effectively the amount of data it can send and still remain within its Expected Bandwidth. Bandwidth Credit is the Bandwidth Allowance less the Bandwidth Used accumulated over time.

Bandwidth Credit is calculated for each virtual channel as follows:

$$BandwidthCredit = \sum_{Frames} \frac{BandwidthAllowance - UsedBandwidth}{Expected}$$

Where Used Bandwidth is the amount of data sent by a particular virtual channel in the last data frame, which is zero except for all virtual channels except for the one that sent the last frame.

The Bandwidth Credit is updated every time a data frame for any virtual channel has been sent. A Bandwidth Credit value close to zero indicates nominal use of bandwidth by the virtual channel. A negative value indicates that the virtual channel is using more than its expected amount of link bandwidth. A positive value indicates that the virtual channel is using less than its expected amount of link bandwidth.

To simplify the hardware required to calculate the Bandwidth Credit it is allowed to saturate at plus or minus a Bandwidth Credit Limit, i.e. if the Bandwidth Credit reaches a Bandwidth Credit Limit it is set to the value of the Bandwidth Credit Limit.

When the Bandwidth Credit for a virtual channel reaches the negative Bandwidth Credit Limit it indicates that the virtual channel is using more bandwidth than expected. This may be recorded in a status register and used to indicate a possible error condition. A network management application is able to use this information to check correct utilisation of link bandwidth by its various virtual channels.

For a virtual channel supporting bandwidth reserved QoS, the value of the bandwidth counter provides the precedence value for that virtual channel.

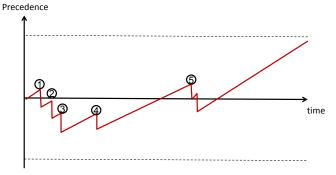

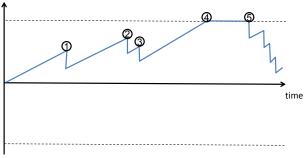

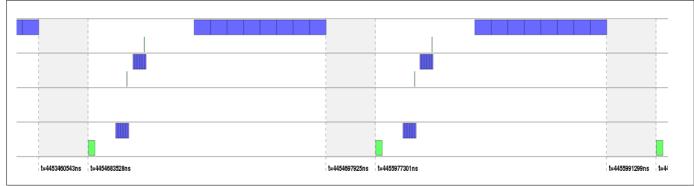

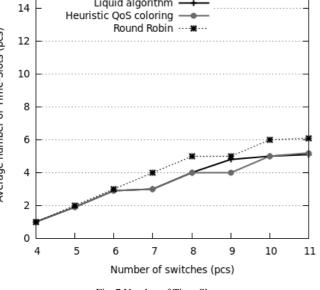

The operation of a bandwidth credit counter is illustrated in Figure 2.

#### Figure 2 Bandwidth Credit Counter

The bandwidth credit for a particular VC increments gradually. At point (1) a frame is sent from by this VC, resulting in a sudden drop in credit. The size of the drop is amount of data sent in the frame divided by the percentage bandwidth reserved for the VC. This means that the smaller the percentage bandwidth the larger the drop, and hence the longer it takes to regain bandwidth credit.

After the drop at point (1) the bandwidth credit gradually increments until point (2) when another frame is sent by the VC. Further frames are sent at points (3), (4), (5) etc. If the frames sent are full frames then the drop in bandwidth credit every time a frame is sent, will be the same size.

The bandwidth credit counter for another VC is illustrated in Figure 3. This VC has about half the bandwidth of the VC in Figure 2 allocated to it. This means that the drops in bandwidth credit when frames are sent by this VC are about twice the size, as can be seen Figure 3 at points (1), (2) and (3).

Precedence

#### Figure 3 Bandwidth Credit Counter with Smaller Reserved Bandwidth

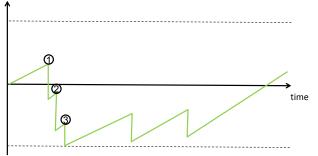

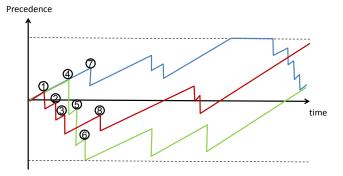

The bandwidth credit counter of another VC is shown in Figure 4. In this case the bandwidth credit slowly increments and although some frames are sent at points (1), (2) and (3), the bandwidth credit eventually saturates, reaching its maximum permitted value at point (4). Although more bandwidth should be accumulated after point (4) this is effectively ignored since the maximum possible bandwidth credit has been reached. At point (5) a frame is sent once more, resulting in a drop from the maximum bandwidth credit value.

Precedence

#### Figure 4 Bandwidth Credit Counter Reaching Saturation

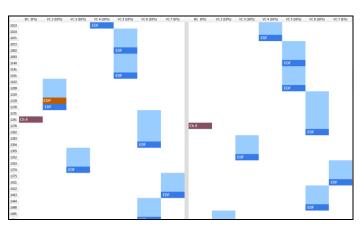

All three VCs are shown together in Figure 5. When a VC has a data frame ready to send and room for a full data frame at the other end of the link, it competes with any other VCs in a similar state, the one with the highest bandwidth credit being allowed to send the next data frame. At points (1), (2) and (3) the red VC has data to send and sends frames. At points (4), (5) and (6) the green VC has data to send and sends a data frame. At point (7) both the blue and the red VCs have data to send. The blue VC wins since it has the highest bandwidth credit count. After this the red VC is allowed to send a further data frame at point (8).

#### Figure 5 Bandwidth Credit of Competing VCs

If the bandwidth credit counter reaches the minimum possible bandwidth credit value, it indicates that it is using more bandwidth than expected and a possible error may be flagged. This condition may be used to stop the VC sending any more data until it recovers some bandwidth credit, to help with "babbling idiot" protection.

Similarly if the bandwidth credit counter stays at the maximum possible bandwidth credit value for a relatively long period of time, the VC is using less bandwidth than expected and this condition can be flagged to indicate a possible error.

The bandwidth credit value is the precedence used by the medium access controller to determine which VC is permitted to send the next data frame.

#### D. Priority

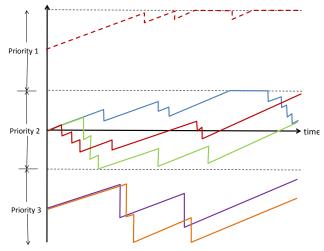

The second type of QoS provided by VCs is priority. Each VC is assigned a priority value and the VC with the highest priority (lowest priority number) is allowed to send the next data frame as soon as it is ready. Figure 6 shows three priority levels. SpaceFibre has 16 priority levels.

Figure 6 Multi-Layered Precedence Priority QoS

Within any level there can be any number of VCs which compete amongst themselves based on their bandwidth credit. A higher priority VC will always have precedence over a lower priority VC unless its Bandwidth Credit has reached the minimum credit limit in which case it is no longer allowed to send any more data frames. This prevents a high priority VC from consuming all the link bandwidth if it fails and starts babbling. More than one VC can be set to the same priority level in which case those VC's will compete for medium access using bandwidth reservation.

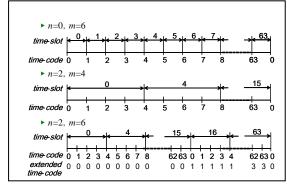

#### 6.5 Scheduled

To provide fully deterministic data delivery it is necessary for the QoS mechanism to ensure that data from specific virtual channels can be sent (and delivered) at particular times. This can be done by chopping time into a series of time-slots, during which a particular VC is permitted to send data frames. This is illustrated in Figure 7.

| Time-slot | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

|-----------|---|---|---|---|---|---|---|---|

| VC 1      |   |   |   |   |   |   |   |   |

| VC 2      |   |   |   |   |   |   |   |   |

| VC 3      |   |   |   |   |   |   |   |   |

| VC 4      |   |   |   |   |   |   |   |   |

| VC 5      |   |   |   |   |   |   |   |   |

| VC 6      |   |   |   |   |   |   |   |   |

| VC 7      |   |   |   |   |   |   |   |   |

| VC 8      |   |   |   |   |   |   |   |   |

#### Figure 7 Scheduled Quality of Service

Each VC is allocated one or more time-slots in which it is permitted to send data frames. VC1 is scheduled to send in time-slot 1 and VC2 is scheduled to send in time-slots 2 and 3. The time-slot duration is a system level parameter, typically  $100 \ \mu$ s, and there are 256 time-slots.

During a time-slot, if the VC is scheduled to send in that time-slot, it will compete with other VCs also scheduled to send in that time-slot based on precedence (priority and bandwidth credit). A fully deterministic system would have one VC allowed to send in a time-slot.

The schedule is always operating. If a user does not want to use scheduling the schedule table is simply filled completely, allowing any VC to send in any time-slot, competing with precedence.

Scheduling can waste bandwidth if only one VC is allowed to send in a time-slot and that VC is not ready. To avoid this situation, the critical VC can be allocated a time-slot and given high priority. Another VC can be allocated the same time-slot with lower priority. In this way when that time-slot arrives the high priority VC will be allowed to send its data, but if it is not ready the VC with lower priority can send some data. This configuration is illustrated in Figure 7 time-slot 3 and VCs 6 and 8.

Time-slots can be defined using broadcast messages to send start of time-slot signals or to send time information and having a local time counter which determines the start and end of each time-slot. The SpaceFibre broadcast message mechanism support both synchronisation and time distribution.

The SpaceFibre QoS mechanism is simple and efficient to implement and it provides bandwidth reservation, priority and scheduling integrated together, not as separate options. Furthermore SpaceFibre QoS provides a means for detecting "babbling idiots" and for detecting nodes that have ceased sending data when they are expected to be sending information.

### IV. SPACEFIBRE FAULT DETECTION, ISOLATION AND RECOVERY

SpaceFibre provides automatic fault detection, isolation and recovery. When a fault occurs on a SpaceFibre link, it is detected and the erroneous or missing information resent. SpaceFibre recovers from intermittent faults very rapidly, detecting faults, recovering and resending data faster than SpaceWire disconnects and reconnects a link. The retry mechanism does not depend on time-outs, naturally adapting to different cable delays.

Fault detection is provided by checking each 8B/10B symbol for disparity errors and invalid 8B/10B codes. SpaceFibre has selected the 8B/10B K-codes it uses to have enhanced Hamming distance from data-codes. This means that a single bit error occurring in a data-code cannot result in a valid K-code used by SpaceFibre. In addition each data frame, broadcast frame, FCT, ACK and NACK are protected by a CRC.

Fault isolation is provided at various levels in SpaceFibre. AC coupling is used in the physical layer to prevent damage from faults that cause DC voltages exceeding the maximum permitted to appear on the transmitter outputs or receiver inputs. This feature also enables galvanic isolation to be implemented readily. At the Quality level SpaceFibre provides time containment, containing errors in the data frame in which they occur, and bandwidth containment, containing errors to the virtual channel in which they occur; an error in one VC does not affect data flowing in another VC. Babbling idiots are contained using the QoS mechanism described above.

Fault recovery is provided at the link level using a retry mechanism that resends data frames, broadcast frames and FCTs. The retry is very fast, uses a minimum amount of buffer memory, and adapts automatically to different link lengths. In addition to the retry mechanism the multi-lane functionality includes graceful degradation on lane failure. If a lane fails permanently, so that a retry or re-initialisation does not recover lane operation, a multi-lane system will continue using the remaining lanes available. This reduces the bandwidth available but does not stop the link operating. For critical operations an extra lane can be included and the graceful degradation will then provide automatic replacement of a faulty lane. The bit error rate (BER) of a lane is monitored and a lane reported as faulty if the (BER) is above a level which results in the effective link bandwidth being unusable. This feature allows lanes that can re-initialise successfully but which will not run for very long before having to re-initialise again, to be detected, isolated and replace by a fully functional lane.

#### V. SPACEFIBRE NETWORKS

A SpaceFibre network uses similar packet formats, packet addressing and routing concepts to SpaceWire. The main difference is that SpaceFibre includes virtual channels.

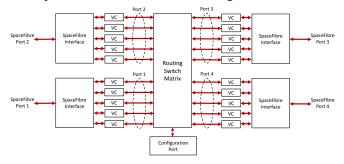

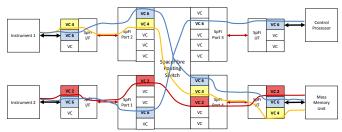

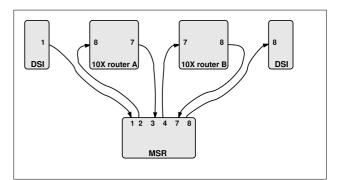

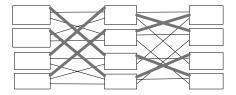

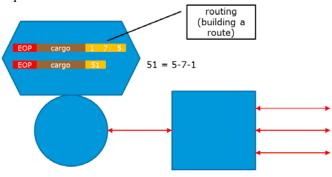

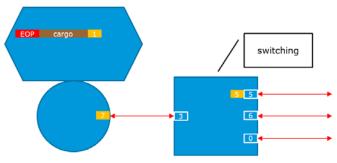

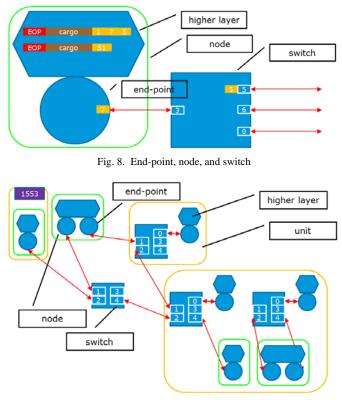

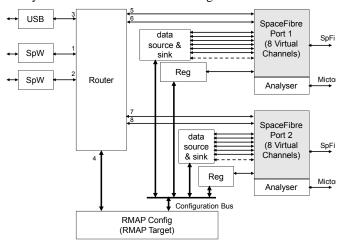

A SpaceFibre router is illustrated in Figure 8.

Figure 8 SpaceFibre Router

The SpaceFibre router comprises a number of SpaceFibre interfaces and a routing switch matrix. Each SpaceFibre interface has several virtual channels. The VC number for each virtual channel can be configured, except for VC0 which is a virtual channel used for configuration, control and monitoring of the SpaceFibre network. When a packet arrives on a SpaceFibre interface it is placed in the appropriate virtual channel, i.e. the one with the same VC number as it was transmitted on. The leading data character of the packet determines which port of the routing switch the packet is to be forwarded through using either path or logical addressing. The port that it is to be switched to must have a VC configured with the same number as the VC that the packet arrived on. The packet is then passed through the routing switch matrix and placed frame by frame in the VC of the output port. The packet is then transferred across the SpaceFibre link, competing with other VCs in that port for access to the link medium according to their precedence.

If a packet arrives and the output port that the packet is to be switched to does not have a VC with the same number as that on which it arrived, the packet is spilt and an error recorded.

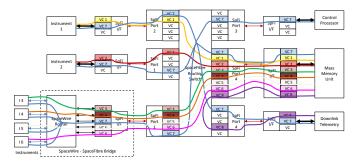

Virtual channels can be used to construct virtual networks where a single VC number is used for connecting to all or several of the nodes attached to the network. This is illustrated in Figure 9 where VC6 (blue) is used to connect all the nodes on the network. Using VC6 the Control Processor can send commands to Instrument 1 or 2 or the Mass Memory unit, setting their operating mode or reading housekeeping information, etc. This virtual network acts like a SpaceWire network.

Figure 9 A Simple SpaceFibre Network

Virtual channels can also be used to construct virtual point to point links from one node to another. VC2 and VC4, in Figure 9, are providing virtual point to point links. VC2 provides a virtual point to point link between Instrument 2 and the Mass Memory Unit and VC4 between Instrument 1 and the Mass Memory. These virtual channels can be each allocated the bandwidth they need to send their data to the Mass Memory Unit. Once this bandwidth is allocated other virtual channels or virtual networks will not interfere with their operation.

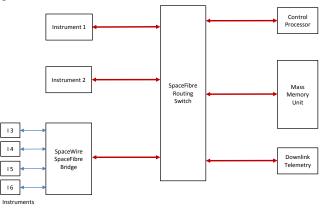

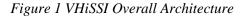

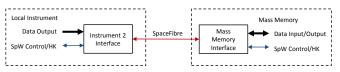

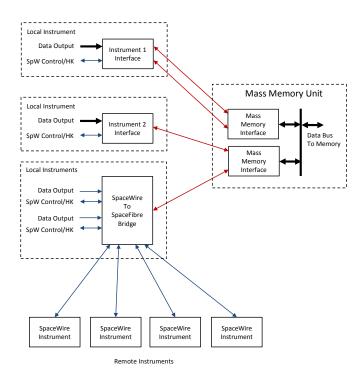

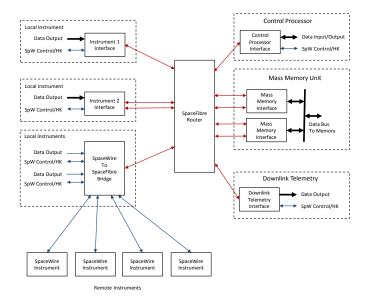

Figure 10 shows a more realistic onboard network using SpaceFibre which includes a SpaceWire to SpaceFibre Bridge. Two high data-rate instruments (Instruments 1 and 2) have SpaceFibre connections. Four less demanding instruments have SpaceWire connections to the SpaceWire to SpaceFibre Bridge. Each instrument has a virtual point to point connection to the Mass Memory Unit and there is a virtual point to point connection between the Mass Memory and the Downlink Telemetry Unit. The Control Processor has a virtual network for configuring and controlling all devices on the network.

Figure 10 Realistic SpaceFibre Network

Figure 10 is solving a complex communication task with many separate, isolated virtual channels providing point to point links, and a virtual network being used to control the entire system. Figure 11 shows this same network with the virtual channels removed, revealing the simplicity of implementation of a complex communication task when using SpaceFibre.

Figure 11 Simple System Architecture with SpaceFibre

#### VI. SPACEFIBRE IMPLEMENTATIONS

The SpaceFibre specification has been written by the University of Dundee for ESA, and has been widely reviewed by the international spacecraft engineering community. It has also been simulated and implemented in several forms. While work remains to be done on the specification the existing draft specification is close to maturity. In this section the current state of SpaceFibre is explored.

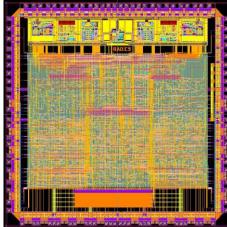

A SpaceFibre interface has been designed by University of Dundee and STAR-Dundee for ESA. This VHDL IP core has been used at all stages of the draft specification to validate and prove the concepts being explored. As a consequence the VHDL IP core has gone through as many iterations as the SpaceFibre specification. At present the VHDL IP core implements all layers of the SpaceFibre specification with the exception of the Multi-Lane layer.

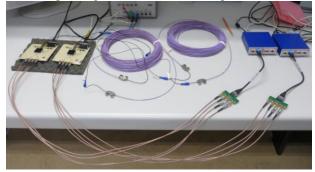

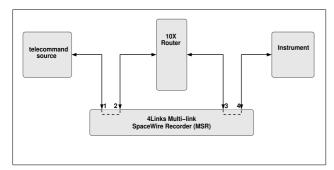

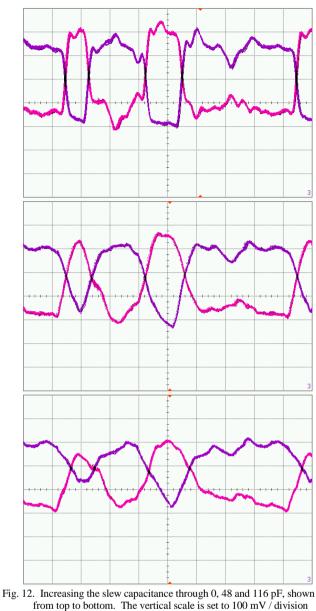

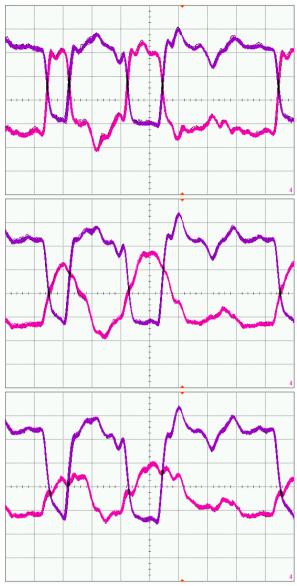

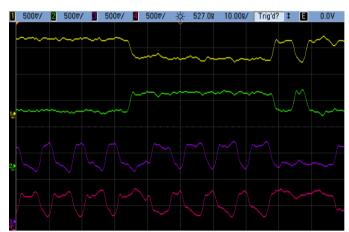

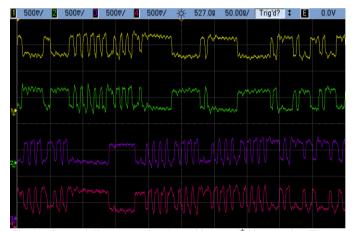

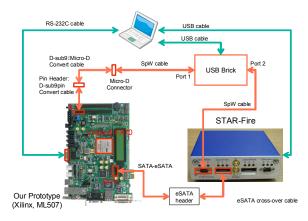

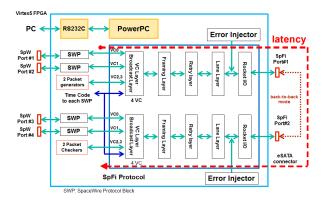

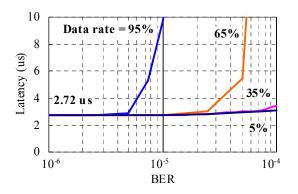

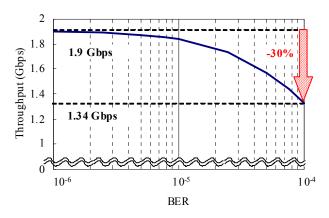

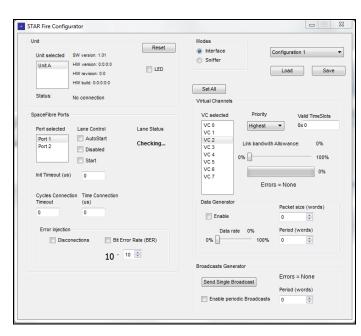

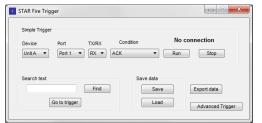

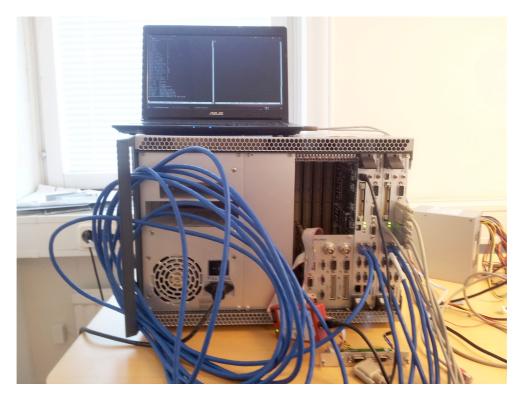

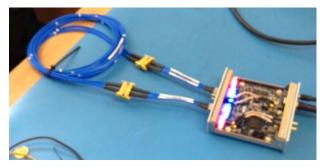

To support the testing of SpaceFibre a suitable test platform was required, so STAR-Dundee developed the STAR Fire unit, which has two SpaceFibre interfaces and includes a link diagnostic capability for analysing traffic on a SpaceFibre link. Two STAR Fire units are being used in Figure 12 to help with the testing of radiation tolerant Fibre Optic transceivers for SpaceFibre operating over 100 m of Fibre Optic cable.

Figure 12 STAR Fire Testing 100m Fibre Optic Cable

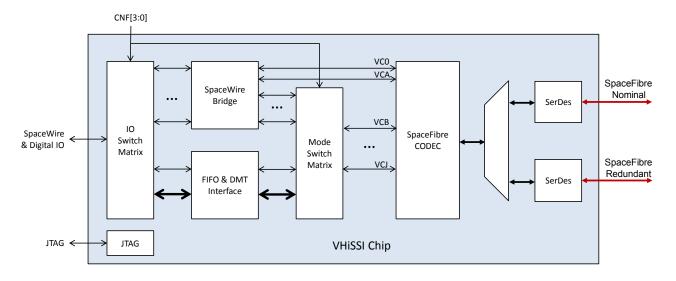

A radiation tolerant SpaceFibre interface device (VHiSSI) is being developed by University of Dundee and several partners within a European Union (EU) Framework 7 project [6].

NEC and Melco are both developing SpaceFibre interface devices to the specification produced by the University of Dundee. This work is providing valuable feedback on the specification and implementation of SpaceFibre. Interoperability testing in December 2013 and April 2013 has been successful with various levels of the SpaceFibre protocol stack being implemented and tested.

Research carried out during the SpaceWire-RT EU Framework 7 project resulted in the Quality layer for SpaceFibre being developed by University of Dundee. Within this same project St. Petersburg University of Aerospace Instrumentation (SUAI) modelled and simulated the various layers of SpaceFibre and ELVEES assessed the feasibility of ASIC implementation using a custom designed SerDes.

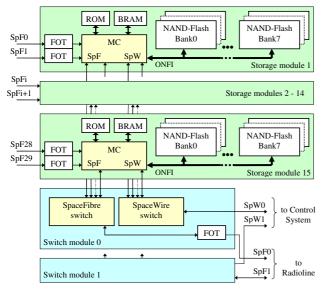

Several ESA projects are using the Dundee SpaceFibre IP core under a Beta evaluation programme including:

- High Performance COTS Based Computer, Astrium and CGS.

- Leon with Fast Fourier Transform Co-processor, SSBV.

- FPGA Based Generic Module and Dynamic Reconfigurator, Bielefeld University.

- Next Generation Mass Memory, Astrium, IDA and University of Dundee.

- 1 x High Processing Power DSP, Astrium and STAR-Dundee.

Work on the formal European Cooperation for Space Standardization (ECSS) standard for SpaceFibre is schedule to start in early 2014, once the technical specification is complete.

#### VII. CONCLUSIONS

SpaceFibre is a multi-gigabit/s networking technology designed specifically for spaceflight applications. It incorporates a comprehensive quality of service capability providing integrated bandwidth reservation, priority and scheduling. Efficient, effective and rapid fault detection, isolation and recovery mechanisms are included in the SpaceFibre interface, enabling rapid detection and recovery from link level errors.

SpaceFibre is designed to support very high data-rate missions like multi-spectral imagers and synthetic aperture radar. It reduces development time and costs, because of its integrated QoS and FDIR capabilities and because it simplifies previously complex onboard data-handling architectures. SpaceFibre is designed to use the same packet format as SpaceWire enabling straightforward upgrading of spacecraft networks to include the improved QoS, FDIR and bandwidth of SpaceFibre while being able to operate with existing SpaceWire equipment. SpaceWire units can be readily integrated with SpaceFibre using a SpaceWire to SpaceFibre Bridge.

#### ACKNOWLEDGMENT

The research leading to these results has received funding the European Space Agency under ESA contract numbers 4000102641 and from the European Union Seventh Framework Programme (FP7/2007-2013) under grant agreement n° 263148 and 284389. We would also like to thank Martin Suess the ESA project manager for the SpaceFibre related activities for his help, advice and guidance.

#### REFERENCES

- S. Parkes, A. Ferrer, A. Gonzalez, & C. McClements, "SpaceFibre Standard Draft E1", University of Dundee, 28<sup>th</sup> September 2012.

- [2] S. Parkes, A. Ferrer, A. Gonzalez, & C. McClements, "SpaceFibre: Multiple Gbits/s Network Technology with QoS, FDIR and SpaceWire Packet Transfer Capabilities", International SpaceWire Conference, Gothenburg, June 2013.

- [3] S. Parkes, "Never Mind the Quality, Feel the Bandwidth: Quality of Service Drivers for Future Onboard Communication Networks", paper no. IAC-10.B2.6.6, 61<sup>st</sup> International Astronautical Congress, Prague 2010.

- [4] S. Parkes, C. McClements and M. Suess, "SpaceFibre", International SpaceWire Conference, St Petersburg, Russia, 2010, ISBN 978-0-9557196-2-2, pp 41-45.

- [5] ECSS Standard ECSS-E-ST-50-12C, "SpaceWire, Links, Nodes, Routers and Networks", Issue 1, European Cooperation for Space Data Standardization, July 2008.

- [6] S. Parkes, A. Ferrer, A. Gonzalez, C. McClements, R. Ginosar, T Liran, G Sokolov, G Burdo, N Blatt, P Rastetter, M Krstic, A Crescenzio, "A Radiation Tolerant SpaceFibre Interface Device", International SpaceWire Conference, Gothenburg, 2013.

## SpaceFibre Quality of Service and Network Routing

SpaceWire Standardisation, Long Paper

Clifford Kimmery and Stephen Belvin Honeywell International Space Electronic Systems Clearwater, FL, USA clifford.kimmery@honeywell.com, stephen.belvin@honeywell.com

*Abstract*— The available SpaceFibre literature views each SpaceFibre virtual channel as logically equivalent to a SpaceWire physical link. This view can be interpreted as allowing SpaceWire packet traversal of the SpaceFibre network through any appropriate virtual channel. Because SpaceWire packets do not have associated Quality of Service (QoS) attributes, the SpaceFibre Standard Draft [1] associates QoS attributes with virtual channels. As a result, SpaceFibre routers must make routing decisions using a combination of SpaceWire packet header and virtual channel QoS attributes to provide a consistent QoS from source to destination. Parkes and Suess [2] introduce the concept of a SpaceFibre virtual network composed of virtual channels with identical Virtual Channel Identifier (VCID) and QoS attributes such that packet routing can be performed using the SpaceWire packet header and the VCID.

While the virtual network concept is beneficial for providing routes with the same QoS attributes through the SpaceFibre network, the mechanisms used should have the flexibility to address the majority of application use cases. In particular, the solution must address the likelihood that some SpaceFibre endpoint implementations will support a small number of virtual channels (for example, one or two). Mapping the resulting collection of virtual networks onto the SpaceFibre network is likely to be a significant problem for larger networks.

We consider the limitations imposed on SpaceFibre network routing by the coupling of VCIDs with virtual networks. We also review possible methods for addressing the limitations identified.

*Index Terms*—SpaceFibre, SpaceWire, network, routing, quality of service, virtual channel, virtual network.

#### I. INTRODUCTION

The introduction of Virtual Channels and Quality of Service (QoS) in SpaceFibre is a significant advancement for the SpaceWire community. The new capabilities also increase the complexity of networks based on SpaceFibre protocols. The concept of establishing virtual networks to provide customized performance capabilities for each network traffic type introduces an abstraction that makes SpaceFibre network routing easier to contemplate and accomplish. By associating a QoS type (we define a QoS type as a specific set of QoS attributes) with each virtual network (VN), network users can view the physical SpaceFibre network as a collection of virtual SpaceWire networks. Each virtual SpaceWire network offers specific network performance characteristics established by the associated QoS type.

#### II. OVERVIEW OF SPACEFIBRE VIRTUAL CHANNELS AND QUALITY OF SERVICE

Virtual channels are fundamental to the SpaceFibre architecture and form the basis for any concept of SpaceFibre networks. A virtual channel is a unidirectional logical link through a physical SpaceFibre link between two nodes. Multiple virtual channels can share a single SpaceFibre physical link. Each virtual channel has independent flow control and behaves like a traditional SpaceWire physical link. Because of the unidirectional nature of SpaceFibre virtual channels, the number of virtual channels operating in one direction can be different than the number operating in the other direction. This capability offers significant flexibility to SpaceFibre network designers.

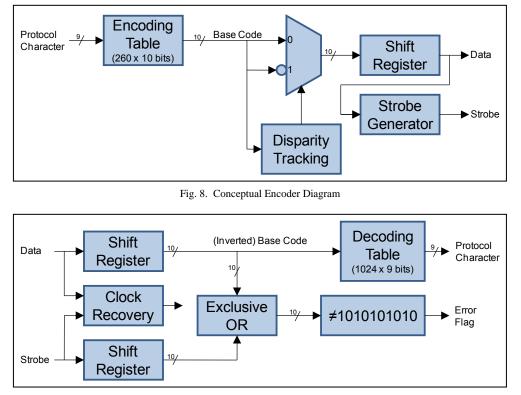

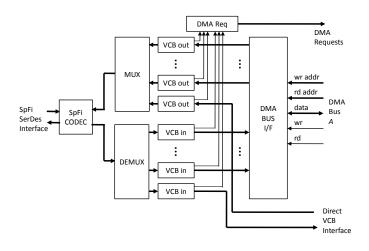

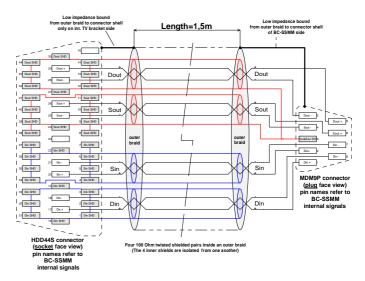

Each SpaceFibre Encoder/Decoder (CODEC) implementation must provide no less than one virtual channel (up to a maximum of 256). A SpaceFibre CODEC must include a Virtual Channel Buffer (VCB) for each Virtual Channel (VC) supported. The SpaceFibre link provides flow control and other link management support by associating a Virtual Channel Identifier (VCID) with each virtual channel. SpaceFibre frames transmitted by the link encoder are associated with the virtual channel by including the VCID in the frame header. A SpaceFibre data frame is shown in Fig. 1 with the header consisting of COMMA, Start of Data Frame (SDF) and VC characters. The frame trailer consists of an End of Data Frame (EDF), Frame Sequence (FR SEQ#) and CRC.

| 0 7       | 8 15    | 16 23  | 24 31     |  |

|-----------|---------|--------|-----------|--|

| СОММА     | SDF     | VC     | RESERVED  |  |

| DATA 1 LS | DATA 1  | DATA 1 | DATA 1 MS |  |

| DATA 2 LS | DATA 2  | DATA 2 | DATA 2 MS |  |

| •••       | •••     | •••    | •••       |  |

| DATA N LS | DATA N  | DATA N | DATA N MS |  |

| EDF       | FR_SEQ# | CRC_LS | CRC_MS    |  |

|           | •       |        |           |  |

Fig. 1. SpaceFibre Data Frame Format.

One of the key benefits of SpaceFibre is support for Quality of Service behaviors. Each QoS behavior defines a mechanism for ensuring that a defined set of network performance characteristics are met. Because SpaceWire packets do not have associated Quality of Service attributes, the SpaceFibre Standard Draft associates QoS attributes with virtual channels. SpaceWire packets traversing a SpaceFibre link are prioritized based on the QoS attributes of the virtual channel. The QoS behavior is established for each virtual channel at the SpaceFibre link transmitter while the link receiver treats all virtual channels equally.

The SpaceFibre Standard Draft defines four QoS behaviors: best effort, priority, bandwidth reservation and scheduled. The Medium Access Controller (MAC) in the SpaceFibre CODEC uses the precedence of each virtual channel to prioritize data transmission. The best effort QoS behavior is assigned the lowest precedence and is dependent on the availability of unallocated link bandwidth to allow packets to traverse the network. The priority QoS behavior defines 16 levels of priority and the SpaceFibre Standard Draft assigns a specific precedence to each level. The best effort QoS is equivalent to lowest precedence level of the priority QoS.

The bandwidth reservation and scheduled QoS behaviors are more complex than the best effort and priority behaviors. In order to determine the precedence of a virtual channel with the bandwidth reserved QoS behavior, the MAC must consider the expected bandwidth utilization of the virtual channel, along with its recently utilized bandwidth and the available link bandwidth. The scheduled QoS behavior is based on fixed time periods or slots, where a virtual channel may be configured to transmit frames in one or more time slots. Priority may be combined with bandwidth reservation or scheduled QoS to provide more control over precedence for a virtual channel.

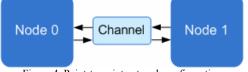

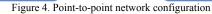

#### **III. SPACEFIBRE NETWORK CONCEPTS**

Much of the existing SpaceFibre literature envisions using SpaceFibre links in point-to-point applications. The focus on single-link applications is appropriate since the SpaceFibre Standard Draft does not address network-level aspects. While some work [2] [3] [4] has considered the application of SpaceFibre to general networks, many aspects remain unresolved.

Earlier work on QoS in SpaceFibre networks [4] has shown the difficulties derived from a lack of QoS attributes associated with SpaceWire packets. Two alternatives for associating QoS attributes with SpaceWire packets traversing SpaceFibre networks were discussed. The first, association of QoS with each virtual channel, is the basis of the method used by the SpaceFibre Standard Draft. The second, including QoS information in the SpaceFibre frame header, offers greater flexibility in network routing at a significant cost in implementation complexity.

The primary disadvantage of associating QoS with the virtual channel is that the number of available VCIDs establishes the upper bound on the number of independent QoS types that can be used in any SpaceFibre link. Recent SpaceFibre work [3] exacerbates this disadvantage by also using the VCID in the SpaceFibre network routing mechanism.

Including QoS attributes within the SpaceFibre frame header has the disadvantage that each SpaceWire packet traversing the virtual channel can dynamically change the QoS attributes of the virtual channel. For the simple QoS types (priority and best effort), this behavior does not have much effect, but for the complex QoS types (bandwidth reservation and scheduled) that are dependent on historical traffic patterns or out-of-band events, such perturbations would be difficult to address.

More recent work [2] [3] defines virtual networks as collections of virtual channels with identical QoS attributes (QoS type). All SpaceWire packet traffic utilizing the virtual network has the same precedence through the physical SpaceFibre network.

In its simplest form, this concept uses virtual SpaceWire networks with topology identical to the physical topology of the host SpaceFibre network. Each virtual network is associated with the QoS attributes needed by one class of SpaceWire traffic used in the system application. For simplicity, each virtual network is allocated a virtual channel in both directions of each SpaceFibre link. In cases where the packet traffic flows in a single direction through the virtual network, the reverse virtual channel is unused.

The concept can be extended by recognizing that the system application is unlikely to use all of the links of the SpaceFibre physical topology in each of the virtual SpaceWire networks. The unused virtual channels do not need to be allocated physical SpaceFibre link resources, freeing those resources for use by other virtual channels.

There are a number of factors that should be considered to make the virtual SpaceWire network design effort sufficiently flexible and convenient. Initial SpaceFibre network implementations are likely to utilize relatively simple topologies containing few links. These initial versions will be composed from newly developed devices designed for the specific applications. The SpaceFibre community should expect to face the issues that have arisen in the SpaceWire community as more capable devices become available and must be integrated into complex networks with older, lesscapable devices. The SpaceFibre Standard Draft should be developed with the expectation that long-term use will result in similar experiences as technology and applications evolve.

#### IV. SPACEFIBRE NETWORK CONSIDERATIONS

The SpaceFibre Standard Draft [1] does not address network-level topics relevant to SpaceWire packet routing, raising a number of concerns. The recent suggested methods [3] [4] for routing in SpaceFibre networks address some, but not all, of these concerns. We review each concern in this section.

#### A. Practical Implementation Constraints

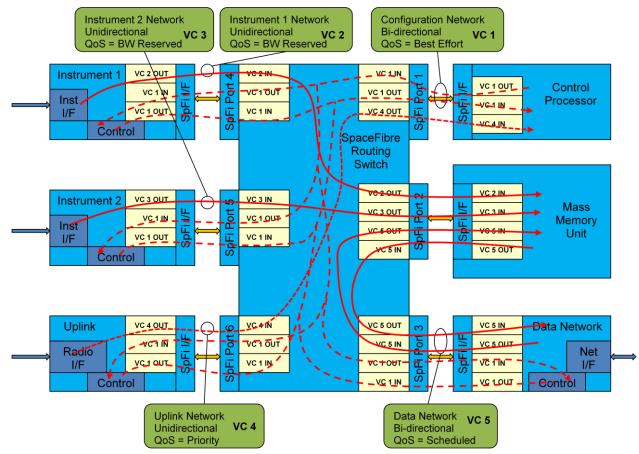

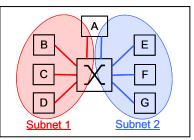

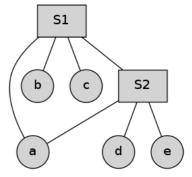

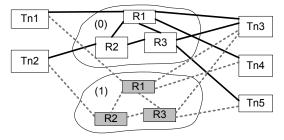

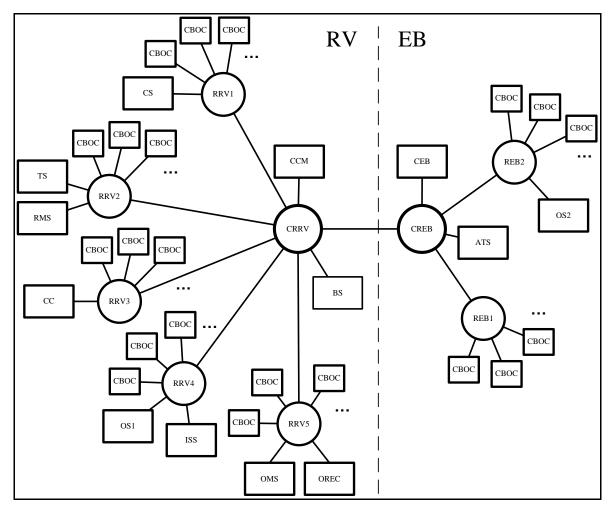

When developing SpaceFibre networks composed of elements with differing levels of VC support, SpaceFibre network designers must assess the many possible mappings of QoS to virtual networks to reach an optimum configuration. In relatively complex cases, achieving a satisfactory result may be dependent on the VC capacity of some network elements. As an example, a network designer can begin by identifying all of the QoS classes needed for the various data flows through the SpaceFibre network. The designer can then define a virtual network for each QoS class by assuming that every network endpoint and router is capable of supporting all of the virtual networks. Figure 2 shows an example on-board data processing system with five SpaceWire VNs identified. The Configuration Network and the Data Network are bidirectional, while the two Instrument Networks and the Uplink Network are unidirectional.

A complete definition of each virtual SpaceWire network requires a detailed inventory of the virtual channels available for each SpaceFibre link. As the number of virtual networks is increased, the ability to optimally provision each VN as desired becomes more difficult. Solutions to such SpaceFibre network optimization problems require the ability to assign virtual channels to an arbitrary virtual network map.

Fig. 2. Virtual Network Identification

#### B. Interoperability of Resource-Constrained Devices

Practical SpaceFibre endpoint and router implementations are likely to minimize the number of distinct virtual channels supported in order to limit complexity and power dissipation characteristics. Such resource-constrained implementations must be allowed to participate in SpaceFibre networks equally with more capable implementations. The SpaceFibre Standard Draft should not impose requirements that unnecessarily favor one class of device implementation over another.

A SpaceFibre endpoint must provide a virtual channel that supports each QoS type used by the application. Since each application utilizing SpaceFibre endpoints will have unique QoS needs, the number of virtual channels and QoS types supported by any specific SpaceFibre endpoint device will be correspondingly unique. Because of the industry tendency to develop products tailored for a specific application, a wide variety of SpaceFibre endpoint devices with a correspondingly wide mix of capabilities are likely to be developed over time.

#### C. SpaceFibre Network Configuration

The need to associate identical QoS attributes with a virtual channel of each network link traversed by a SpaceWire packet increases the configuration overhead of SpaceFibre networks significantly compared to SpaceWire networks. Each SpaceFibre router and endpoint must be configured with the QoS characteristics of each virtual network it supports. The time needed to configure a SpaceFibre network will scale linearly with the number of network entities to be configured and, separately, with the number of virtual networks to be utilized.

A SpaceFibre link clearly must support at least one virtual channel in one direction to be useful (at least one virtual channel in each direction is the likely minimum implementation). Support for additional virtual channels is an implementation decision that will balance application needs against complexity and power dissipation constraints.

The SpaceFibre Standard Draft is ambiguous regarding VCID configuration. The likely interpretation is that the VCID can be written only once after the CODEC exits the cold-reset state. SpaceWire Working Group presentations [3] are consistent with that interpretation. The ambiguity is exacerbated by the fact that each VCB configuration defaults to a VCID of zero. There doesn't appear to be any mechanism to guarantee virtual channel uniqueness (avoid multiple virtual channels with the same VCID, etc.).

The SpaceFibre Standard Draft does not establish mechanisms for negotiating virtual channel use between the ends of a SpaceFibre link. The standard draft apparently presumes that such negotiations are performed using a higher level of the protocol stack. It also does not address the methodology to be followed by compliant implementations when initializing virtual channels. Some concepts [3] assume that VC 0 is always assigned to a Configuration Virtual Network, presumably automatically configured following coldreset to provide full-duplex best-effort access to SpaceFibre network devices.

We can infer that a Flow Control Token (FCT) issued by the link receiver for a specific VCID indicates that the receiver supports that virtual channel. Whether the link transmitter has any obligation to allocate resources to the virtual channel is unclear. Previous negotiation of support for the virtual channel at each end of the link would clearly be beneficial.

The mechanism for initializing virtual channels other than VCID 0 is likely intended to be implemented using a SpaceWire configuration protocol (SpaceWire PnP or similar). While not addressed by the standard, the SpaceFibre CODEC must provide the configuration protocol with a method for determining the available virtual channel capacity. Additionally, the SpaceFibre CODEC at each end of the link must expose the virtual channel configuration fields and provide a mechanism for enabling the virtual channel after configuration is complete.

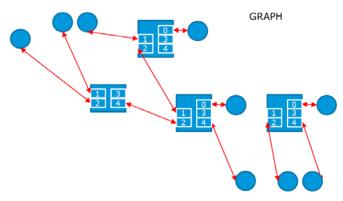

## V. VIRTUAL NETWORKS USING IDENTICAL VIRTUAL CHANNELS

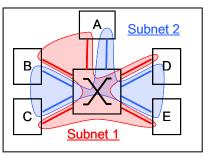

The VCID-based virtual network abstraction [2] [3] offers a conceptually simple method for routing SpaceWire packets over SpaceFibre networks by using the VCID as a substitute for QoS type when making routing decisions. Figure 3 illustrates the concept by showing the use of VCIDs to route SpaceWire traffic through the virtual networks identified in Fig. 2. A virtual channel in every SpaceFibre link used by the virtual network must be assigned the identical VCID regardless of the number of virtual channels supported by the specific SpaceFibre link. Note that routing of SpaceWire packets through the virtual network is performed similarly to traditional SpaceWire routing.

Fig. 3. Packet Routing Based on Virtual Channel Identifier

In the example shown in Fig. 3, the application creating SpaceWire traffic in Instrument 1 sends data to the Mass Memory Unit over the VCID2 virtual network. During network initialization, all of the network endpoints and routers must be configured with identical QoS attributes assigned to every virtual channel with a VCID of 2. Any violation of this rule causes inconsistent QoS behavior within the virtual network. If the application in Instrument 2 were to use the VCID2 virtual network to send packets to the Mass Memory Unit, the router must arbitrate between the two packet streams for access to VC2 of Port 2. When Instrument 2 uses the VCID3 virtual network as shown in Fig. 3, the router simply forwards the packets over the respective virtual channels of Port 2.

#### A. Limits on the Number of Virtual Networks

As mentioned in previous work [4], using the VCID as a QoS type identifier limits the number of QoS types that can be mapped onto the physical SpaceFibre link. By extension, using the VCID as a virtual network identifier limits the number of virtual SpaceWire networks that can be mapped onto the physical SpaceFibre network. While not a concern for the SpaceFibre networks considered in currently proposed applications, future SpaceFibre applications are likely to impose much more complex scenarios.

The number of virtual networks mapped to a physical network can be increased beyond the limit of 256 VCIDs in cases where a VCID can be used to identify multiple virtual networks. Such cases only arise if certain virtual networks have non-overlapping footprints within the overall physical network. The definition of non-overlapping virtual networks is dependent on the ability to establish isolation boundaries within the physical SpaceFibre fabric. An isolation boundary prevents SpaceWire packets on one virtual network from bleeding into a different virtual network when both virtual networks have the same VCID.

#### B. Virtual Channel Initialization

The SpaceFibre Standard Draft requires that SpaceFibre CODECs establish the VCID associated with each VCB after cold reset. The QoS parameters associated with a VCID are configurable using the CODEC link management interface. The VCID-based virtual network abstraction requires that assignment of the VCID be accomplished during network configuration.

#### C. Initial Virtual Channel Identifier Assignment

If simple SpaceFibre CODEC implementations statically assign the VCID of each virtual channel supported (sequential integers starting at zero, for example), the ability to design complex SpaceFibre networks with more than a few virtual networks is significantly limited. To support the VCID-based virtual network abstraction, any individual SpaceFibre endpoint might need to connect to multiple non-contiguous virtual networks within the VCID state space.

#### D. Virtual Channel Identifier Reassignment

Since a physical SpaceFibre network can be composed of many virtual SpaceWire networks, an endpoint containing a small number of virtual channels would benefit from the ability to dynamically connect and disconnect to any arbitrary virtual SpaceWire network desired. To support the VCID-based virtual network abstraction, such a capability would require reconfiguring a virtual channel to match the QoS attributes and VCID of the desired network. Since the virtual channel reconfiguration must be performed at both ends of the SpaceFibre link, the most appropriate method involves taking the virtual channel offline, reconfiguring each end of the link and bringing the virtual channel back online.

As currently specified in the SpaceFibre Standard Draft, the flow control counters associated with a virtual channel can only be initialized by reset or remote flush (link initialization). These events apparently affect the flow control counters of all virtual channels, making it very difficult to dynamically reassign a single virtual channel to a different virtual network (VCID) without taking the entire SpaceFibre link offline. This limitation is particularly acute for SpaceFibre endpoints with few virtual channels that need to support more QoS classes than the number of virtual channels available.

#### VI. VIRTUAL NETWORKS USING ARBITRARY VIRTUAL CHANNELS

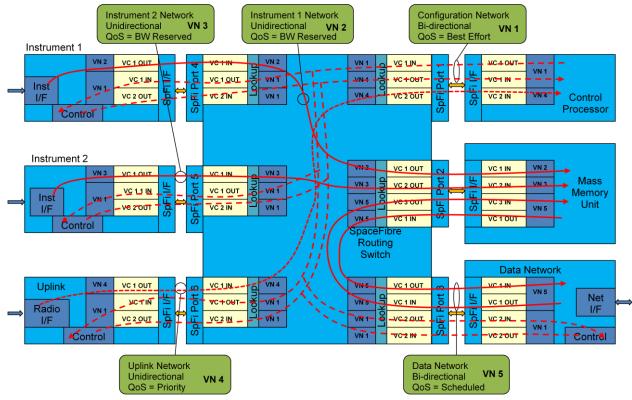

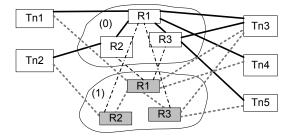

Many of the issues raised regarding virtual networks composed of virtual channels with identical VCIDs can be eliminated by allowing a virtual network to use any virtual channel that has been initialized with the appropriate QoS attributes. Creating virtual networks from arbitrary collections of virtual channels with identical QoS attributes allows much greater network design flexibility.

As previously mentioned, a virtual network is composed of virtual channels with identical QoS attributes. Every virtual channel in the virtual network must be initialized to have the same QoS attributes. The use of virtual channels is greatly simplified by introducing the concept of a Virtual Network Identifier (VNID) that identifies a specific QoS type (combination of QoS attributes).

#### A. Limits on the Number of Virtual Networks

The VNID concept allows practically unlimited scaling of the number of virtual SpaceWire networks that a SpaceFibre network can support. The limit on the number of virtual networks that can simultaneously use a single SpaceFibre link remains, but has little affect on the number of virtual networks that can be globally defined. An additional benefit is the low complexity associated with virtual channel initialization and VCID assignment.

A specific set of QoS attributes is associated with each virtual channel using the corresponding VNID. While a virtual channel must be associated with one VNID, an individual VNID can be associated with more than one VCID on the same link. Note that the number of VNIDs supported by an endpoint device can exceed the number of VCBs available since the QoS attributes of a virtual channel are allowed to change without reinitializing the virtual channel.

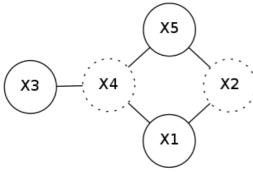

Figure 4 illustrates the concept by showing the SpaceWire traffic routed through virtual networks identified by the VNID. Any virtual channel in a SpaceFibre link can be associated with the virtual network since the VCID is not used for network routing. The SpaceFibre router contains the mapping between the VNID and the associated VCID(s) of each router port. SpaceWire packets entering the router through a virtual channel are sent to the virtual SpaceWire network associated with that virtual channel. The virtual network routes the SpaceWire packets to the output port using traditional SpaceWire routing methods. The packets are transmitted over the output virtual channel associated with the virtual network.

In the example shown in Fig. 4, the application creating SpaceWire traffic in Instrument 1 sends data to the Mass Memory Unit over the VNID2 virtual network. During network initialization, all of the network endpoints and routers must be configured with identical QoS attributes assigned to every virtual channel associated with virtual network VNID2. Any violation of this rule causes inconsistent QoS behavior within the virtual SpaceWire network. When the application in Instrument 2 sends packets to the Mass Memory Unit over the VNID3 virtual network, the router sends the packet that entered over Port 5, VCID 1, out over Port 2, VCID 2. In the same vein, packets traversing the VNID1 (Configuration) virtual network are routed over links using a variety of VCIDs as shown in Fig. 4.

#### B. Initial Virtual Channel Identifier Assignment

Eliminating the use of the VCID as a virtual network identifier returns the VCID to its primary purpose as a linklevel bandwidth allocation mechanism. As such, the VCID associated with a virtual channel has no relevance beyond the CODECs at each end of the SpaceFibre link.

Fig. 4. Packet Routing Based on Virtual Network Identifier.

#### C. Virtual Channel Identifier Reassignment

Similarly, the need for reassigning VCID values is eliminated when the VCID is no longer used for network routing. An application can easily associate a different VNID with any available virtual channel to join another virtual SpaceWire network at will (the VNID reassignment must be applied to both ends of the SpaceFibre link).

#### D. Virtual Network Routing

Using VNIDs for routing decisions in SpaceFibre networks allows SpaceWire packets to traverse any virtual channel of the outbound port with the matching VNID. The complexity of routing decisions is not significantly greater than using VCIDs since the one-to-one mapping of incoming VCID to VNID can be viewed as a form of indirect addressing.

A characteristic of VNID-based routing is that VNID values do not need to be identical throughout the SpaceFibre network. The VNID value assignments in each router are independent of the assignments in any other router. As with VCID-based routing, however, the QoS attributes of an individual virtual SpaceWire network must be configured identically in every router. Note that there are practical benefits to treating the VNID values as virtual network identifiers and assigning them consistently throughout the SpaceFibre network.

#### VII. SPACEFIBRE STANDARD IMPROVEMENTS

We have identified an ambiguity in the SpaceFibre Standard Draft with regard to assignment of the initial VCID value to each virtual channel. In addition, the default VCID value of zero raises concern about the possibility of multiple virtual channels with the same VCID value. There is also a lack of clarity regarding the acceptable methods for negotiating virtual channel utilization between opposite ends of the SpaceFibre link.

#### A. Improvements for Virtual Networks Using Virtual Channel Identifiers

As discussed above, using VCIDs as virtual network identifiers restricts the use of resource-constrained endpoint devices and complicates the virtual network design task for system implementers. In the event that the SpaceFibre community chooses this method for SpaceFibre routing, a number of improvements to the SpaceFibre Standard Draft are appropriate.

#### 1) Virtual Channel Initialization

Clarification of the virtual channel initialization method is important regardless of the SpaceFibre routing mechanism used. It is critical when the virtual channels must be mapped to an arbitrary VCID in order to be associated with a virtual SpaceWire network identified by that VCID.

The SpaceFibre Standard Draft must provide a detailed description of the CODEC features that make virtual channel initialization possible. It should also describe a process for negotiating virtual channel use between the ends of a SpaceFibre link.

#### 2) Virtual Channel Identifier Configuration

Allowing dynamic VCID assignment improves the usability of resource-constrained endpoint devices in complex VCID-based SpaceFibre networks. An application needing to connect to more virtual SpaceWire networks than the attached SpaceFibre link can support should be able to reassign virtual channels to achieve the desired communication flexibility.

To achieve this capability, the SpaceFibre Standard Draft must provide a mechanism for independent reconfiguration of individual virtual channels. This mechanism should include the ability to clear the FCT counters associated with the virtual channel without affecting the operation of other virtual channels.

#### B. Using Virtual Network Identifiers for Virtual Network Routing

The improvements discussed above are generally unnecessary if a level of indirection is added to the virtual network routing mechanism. By identifying virtual SpaceWire networks using the VNID instead of the VCID, any virtual channel (regardless of the assigned VCID) associated with the VNID is a member of the virtual network. There is no longer a need to assign specific VCIDs to virtual channels, so SpaceFibre CODECs can hardwire the VCID of each supported virtual channel.

Because VNID-based virtual SpaceWire networks don't care about the VCID values used, the virtual channel initialization concerns raised above are less serious. The negotiation of virtual channel utilization between opposite ends of the SpaceFibre link can be significantly simplified.

#### VIII. SUMMARY

We believe that virtual SpaceWire networks based on VNID routing mechanisms is the simplest and most flexible solution for implementing SpaceFibre routers. The simple indirection method described makes the design of complex SpaceFibre networks much simpler than alternatives. In addition, the number of virtual SpaceWire networks that can be defined is not unnecessarily limited by the maximum number of virtual channels possible in any single SpaceFibre link.

#### REFERENCES

- S. Parkes, A. Ferrer, A. Gonzalez, and C. McClements, "SpaceFibre Standard draft E1," ECSS-E-ST-50-XXX, 28th September 2012

- [2] S. Parkes and M. Suess, "Mixed SpaceWire SpaceFibre networks," Proceedings of the 4<sup>th</sup> International SpaceWire Conference, November 2011, San Antonio, Texas, p. 144.

- [3] S. Parkes, C. McClements, M. Dunstan, A. Ferrer, and A. Gonzalez, "SpaceFibre," SpaceWire Working Group Meeting 19 Session 1 Revised SpaceFibre specification, October 2012.

- [4] C. Kimmery, "SpaceFibre virtual channels and flow-control," Proceedings of the 2<sup>nd</sup> International SpaceWire Conference, November 2008, Nara, Japan, pp. 37-38.

## GigaSpaceWire – Gigabit Links for SpaceWire Networks

Standardisation, Long Paper

Evgeny Yablokov, Yuriy Sheynin, Elena Suvorova, Alexander Stepanov Institute of High-Performance Computer and Network Technologies St. Petersburg State University of Aerospace Instrumentation St. Petersburg, Russian Federation Evgeny.Yablokov@guap.ru, Sheynin@aanet.ru, Suvorova@aanet.ru, Alexander.Stepanov@guap.ru

Abstract—SpaceWire network technology is intended to be used for spacecraft on-board communication. Providing low implementation and overhead costs as well as hard real-time communication services, currently SpaceWire fails to meet the latest communication system requirements in the fields of data transmission rate, galvanic isolation, cable length and cable mass raised by world-wide space industry. This paper discusses the new physical layer for SpaceWire called GigaSpaceWire which is aimed to make SpaceWire networks satisfying the requirements.

Index Terms—GigaSpaceWire, gigabit links, galvanic isolation, standardisation.

#### I. INTRODUCTION

SpaceWire technology becomes a general interconnection technology in national and international missions. As its applications become more and more diverse, the constraints of SpaceWire limit its usage in next generation demanding missions. In accordance with analyses made by representatives from the Russian and European [1] and US space industries [2], the main SpaceWire problems are: 1) lack of galvanic isolation; 2) cable length is limited to 10 m distance; 3) limited data rates, while gigabit rates are demanded for new missions; 4) lack of QoS that is required for real-time control. New developments to overcome these problems are on the way (e.g. SpaceFibre, SpaceWire-RT). However they are in the course of development (and would be for a couple of years, at least, before would be finally fixed) and their great features would be not free. Overheads for them would be reasonable where they are actually needed and would be a burden where not.

Analysis shows that the first three of four main constraints of SpaceWire could be solved just now without considerable problems and overheads.

In order to enhance link characteristics for SpaceWire networks this paper describes the GigaSpaceWire technology that has been developed by St. Petersburg State University of Aerospace Instrumentation and ELVEES Company. Tatiana Solokhina, Yaroslav Petrichcovitch, Alexander Glushkov, Ilia Alekseev R&D Center ELVEES Company, Moscow, Russia <u>elcore@elvees.com</u>

GigaSpaceWire provides gigabit link technology with longer distances and galvanic isolation capability for SpaceWire networks. The GigaSpaceWire standard has been previously introduced in paper [3] and its specification has been developed [4] and is considered now as a part of the Russian national SpaceWire-based standard draft.

The core principle of GigaSpaceWire technology is to substitute DS encoding scheme with 8b10b encoding which is currently used in a wide number of communication standards, e.g in such as Fibre Channel [5] and Serial RapidIO [6]. Consequently, galvanic isolation can be implemented, the maximum transmission rate can be raised up to 2.5 Gbit/s (5 Gbit/s in future), the maximum cable length can be increased to 100 m with cable mass significantly reduced.

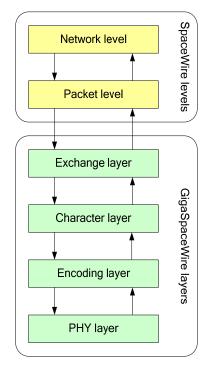

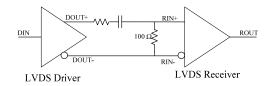

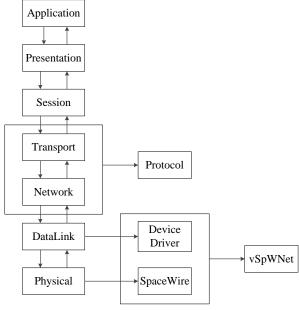

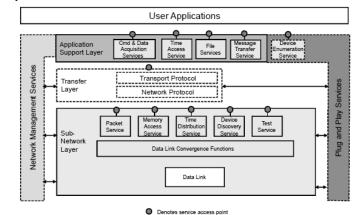

#### II. GIGASPACEWIRE PROTOCOL STACK

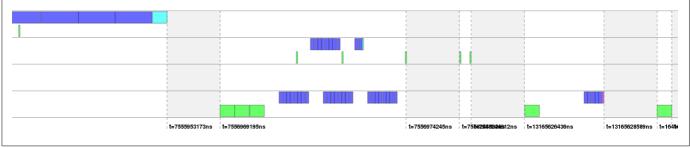

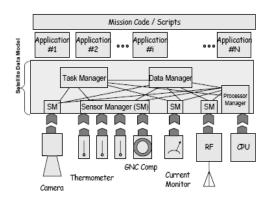

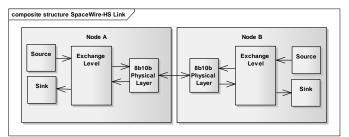

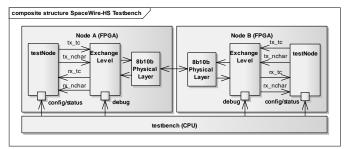

The GigaSpaceWire protocol stack is shown in Fig. 1. It contains new character, encoding and PHY layers, the modified SpaceWire exchange level and the conventional SpaceWire packet and network levels.

The PHY layer principal task is to transmit and receive a raw bit sequence over a physical link. In order to perform it, the PHY layer receiver establishes bit synchronization before starting the reception of data from the link. When bit synchronization is achieved, at the receiving side the PHY layer accepts bit stream from the physical link, performs deserialization and symbol alignment and transmits 10-bit code sequences to the encoding layer. The transmitting side of the PHY layer accepts 10b code sequences from the encoding layer, serializes them and sends bit-wide stream to the physical link.

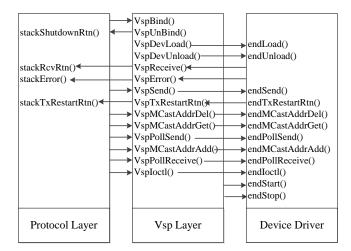

Fig. 1. The GigaSpaceWire protocol stack

The encoding layer performs the 8b10b encoding. At the transmitting side the encoding layer accepts 8b symbols from the character layer and substitutes them with correspondent 10b code sequences. Accordingly, at the receiving side the encoding layer accepts 10b code sequences from the PHY layer and transforms them into 8b symbols.

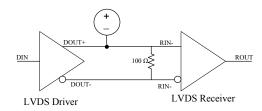

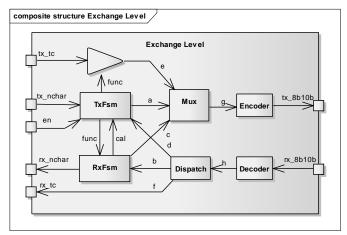

The exchange layer manages the point-to-point connection over the link. After reset the exchange layer tries to establish bi-directional connection with the exchange layer entity of the remote side. If the connection is acquired, the upper layers are allowed to send SpaceWire packets, Time-codes and Distributed Interrupt codes over the link and the exchange layer performs flow control, data rate adjustment and connection maintenance functions. The data stream through the GigaSpaceWire protocol stack is depicted in Fig. 2.

The SpaceWire packet and network levels are not changed. It provides easy GigaSpaceWire links integration into regular SpaceWire networks.

The purpose of the GigaSpaceWire technology is to substitute DS encoding, which is used in the SpaceWire standard, with 8b10b encoding. In turn, it brings to SpaceWire networks such features as possibility for galvanic isolation and long distance data transmission at the rate of several gigabits. However, introduction of the 8b10b encoding into a SpaceWire link causes considerable changes in such basic elements of SpaceWire technology as the exchange level state machine, the silence exchange procedure, the flow control mechanism and the encoding of SpaceWire characters and codes as well as the complete substitution of the signaling and physical levels with the new GigaSpaceWire PHY layer. However, beyond these unavoidable changes the GigaSpaceWire technology does not attempt to introduce new services that are irrelevant to SpaceWire. The principle SpaceWire features that are not affected by GigaSpaceWire are data and control interfaces that link interface offers to the upper layers.

In the following sections the key principles that have been changed in the GigaSpaceWire technology are discussed in detail.

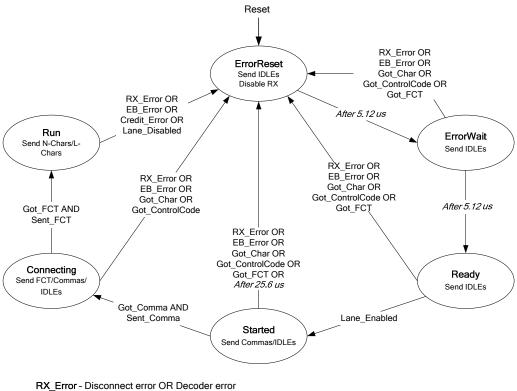

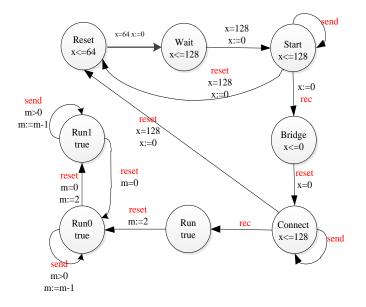

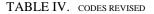

#### III. EXCHANGE LAYER STATE MACHINE

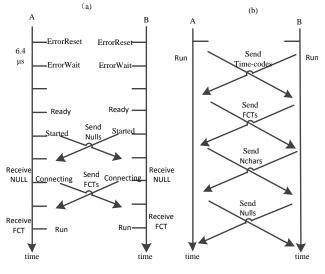

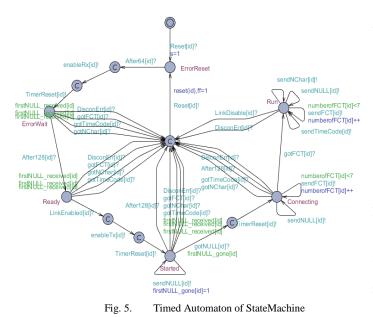

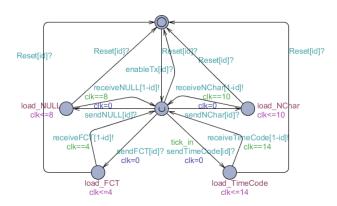

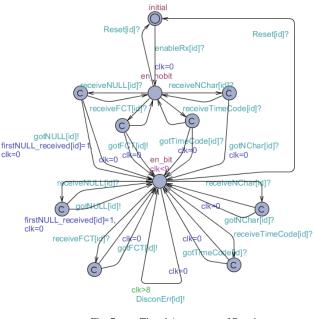

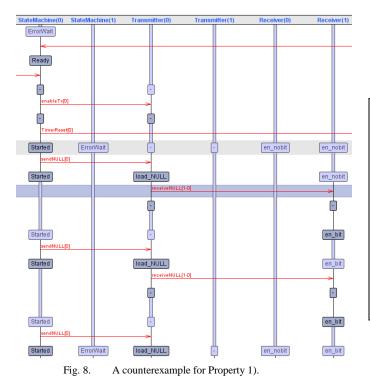

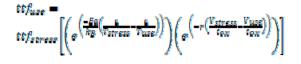

The state machine which is deployed in the GigaSpaceWire exchange layer is given in Fig. 3. The state machine has the same set of states as the SpaceWire exchange level state machine but changes both the rules managing the transmission among the states and operations of transmitter and receiver in particular states.

The most significant difference between the state machines of GigaSpaceWire and SpaceWire consists in the actions that are performed in the ErrorReset, ErrorWait and Ready states. While the PHY layer technology which is incorporated in GigaSpaceWire can require considerable time to make the PHY layer transmitter and receiver ready for communication, the GigaSpaceWire state machine may not disable them each time when the ErrorReset state is entered. Therefore, in order to maintain the bit synchronization and symbol alignment established at the PHY layer, the exchange layer state machine enables the transmitter in all the states. However, in the ErrorReset, ErrorWait and Ready states the transmitter is permitted to send only filler symbols, which are called as IDLE symbols. Simultaneously, the exchange layer receiver is disabled in the ErrorReset state while the PHY layer receiver still operates.

GigaSpaceWire decreases both the 6.4 us and 12.8 us timeouts which manage the transitions from the ErrorReset to the ErrorWait and from the ErrorWait to the Ready states respectively. As in GigaSpaceWire the silence exchange procedure(described below) takes considerably less time and the transmitter and receiver of the PHY layer are never disabled upon entering the ErrorReset state, the durations of both the timeouts are shorted to 5.12 us.

Fig. 2. The GigaSpaceWire data flow

EB\_Error - Elastic buffer error

Fig. 3. The GigaSpaceWire exchange layer state machine

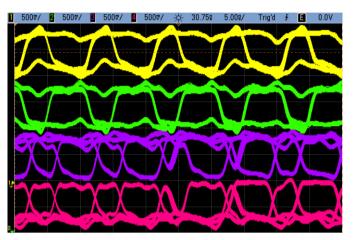

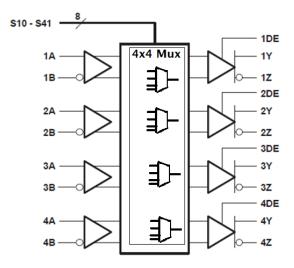

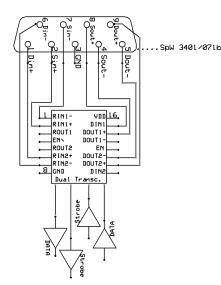

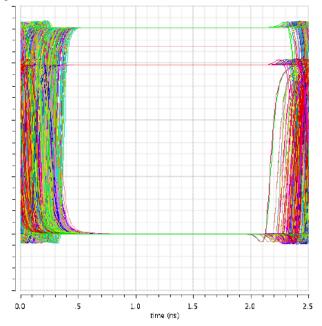

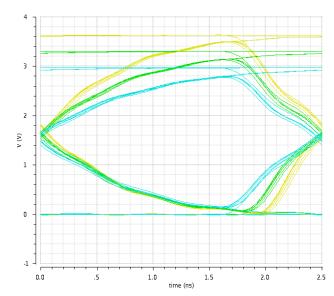

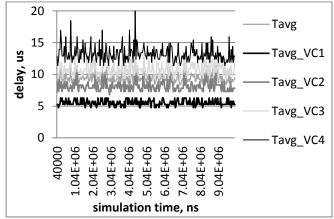

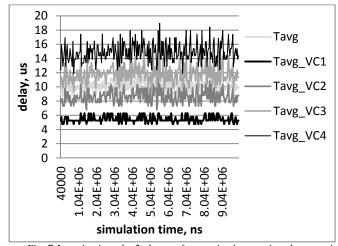

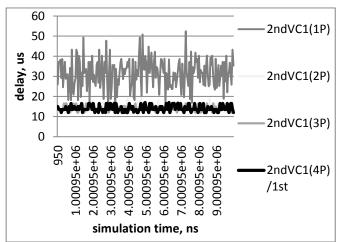

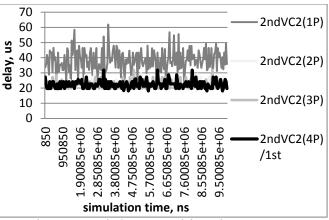

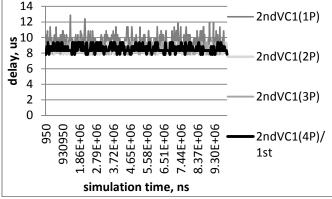

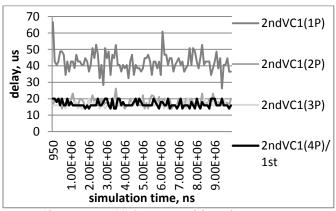

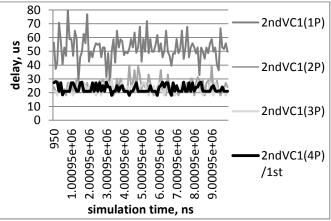

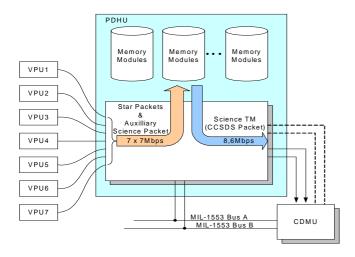

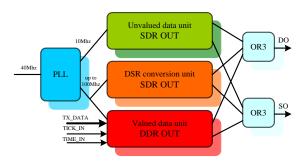

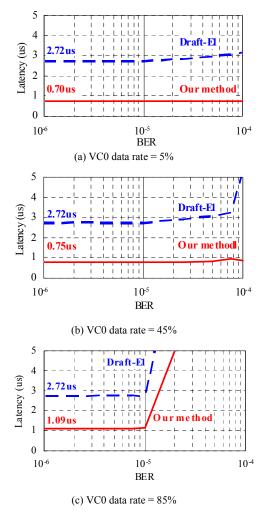

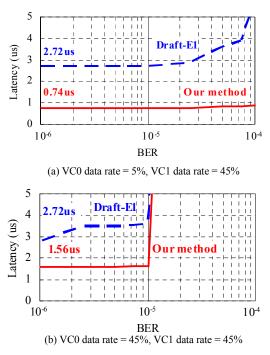

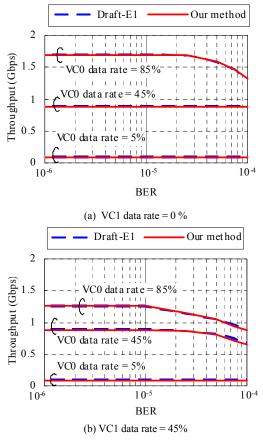

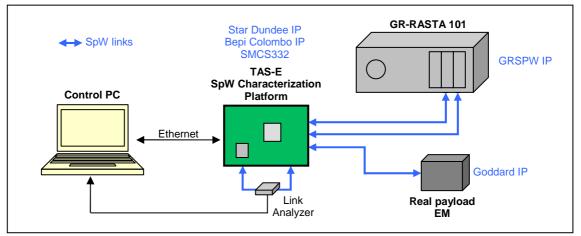

Duration of the timeout in the Started state is increased significantly from 12.8 us to 25.6 us. It is assumed (but not required) that the PHY layer and the exchange layer state machine are enabled simultaneously. Therefore, while powering on the 25.6 us timeout in the Started state is dedicated to provide enough time for both ends of the link to lock PLLs and establish bit synchronization. After the connection at the PHY layer is established, the 25.6 us timeout is not expected to be used.